楞粳

2025-10-15 14:45:00

楞粳

2025-10-15 14:45:00

在刚开始学习FPGA的时候,使用Quartus Prime的GUI界面创建工程是一个再平常不过的事儿,但是随着项目的增多,有很多项目可能会用到之前项目的代码,如果用GUI界面添加代码也可以,但是总觉得这种方法效率太低(点击New Project Wizard->选择工程目录,输入工程名,顶层文件名->添加工程代码及所需的IP文件->选择器件型号->管脚约束……)。

后面在网上找相关的更高效的方法,最终找到了一种使用TCL脚本快速创建Quartus工程的方法,这里直接贴TCL脚本的一个示例:

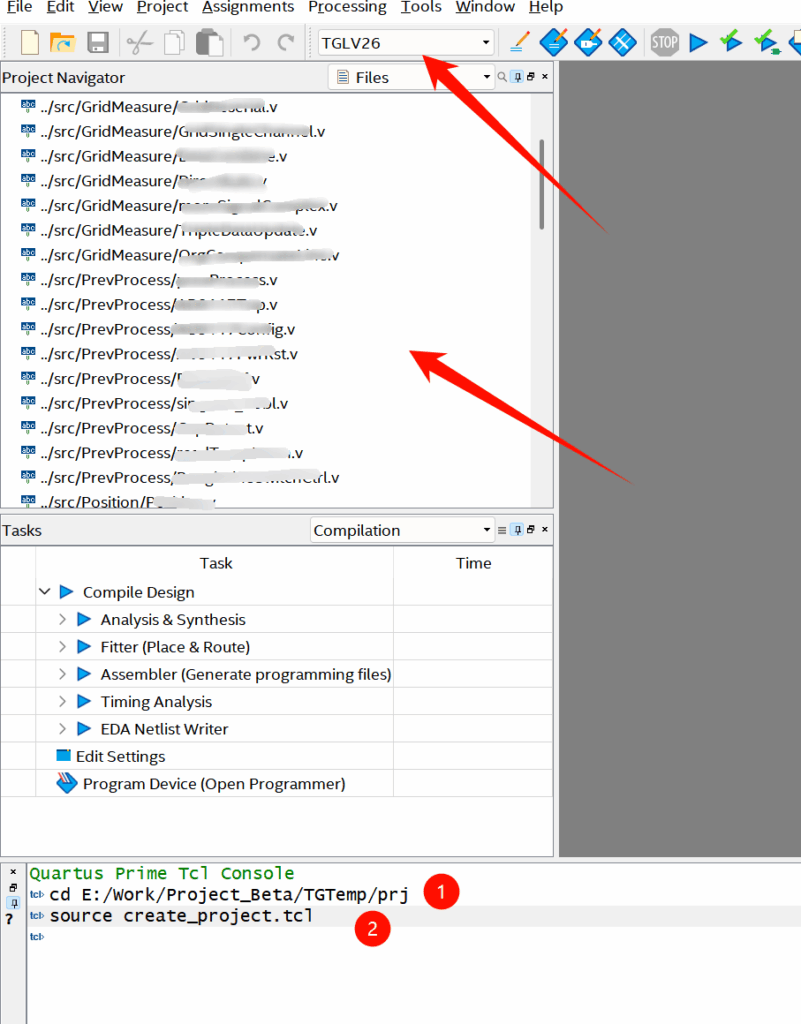

点击查看代码只需创建一个工程文件夹,并在TCL脚本中描述所需的verilog源码文件和IP文件的路径,然后再打开quartus软件,并打开TCL Console窗口,在指令行中输入cd E:/Work/Project_Beta/TGTemp/prj(这里改为脚本所在文件路径),然后输入source xxx.tcl(xxx代表tcl脚本的文件名),即可快速创建工程,具体如下图:

来源:程序园用户自行投稿发布,如果侵权,请联系站长删除

免责声明:如果侵犯了您的权益,请联系站长,我们会及时删除侵权内容,谢谢合作! |

|

|

|

|

|

|

相关推荐

|

|

|